# Armadillo-9 ハードウェアマニュアル

Version 1.1.6 2011/10/21

株式会社アットマークテクノ [http://www.atmark-techno.com]

Armadillo サイト [http://armadillo.atmark-techno.com]

### Armadillo-9 ハードウェアマニュアル

株式会社アットマークテクノ

060-0035 札幌市中央区北 5 条東 2 丁目 AFT ビル TEL 011-207-6550 FAX 011-207-6570

製作著作 © 2004-2011 Atmark Techno, Inc.

Version 1.1.6 2011/10/21

# 目次

| 1. | はじめに                                   | 7  |

|----|----------------------------------------|----|

|    | 1.1. 本書および関連ファイルのバージョンについて             | 7  |

|    | 1.2. 本書の構成                             |    |

| 2  | 注意事項                                   |    |

|    | 2.1. 安全に関する注意事項                        |    |

|    | 2.2. 取扱い上の注意事項                         |    |

|    | 2.3. ソフトウェア使用に関しての注意事項                 |    |

|    |                                        |    |

|    | 2.4. 保証について                            |    |

|    | 2.5. 輸出について                            |    |

|    | 2.6. 商標について                            |    |

| 3. | 概要                                     |    |

|    | 3.1. ボード概要                             | 11 |

|    | 3.2. ブロック図                             | 11 |

| 4. | メモリマップ                                 |    |

|    | ・                                      |    |

|    | 4.2. Linux 使用時の論理メモリマップ                |    |

| 5  | 各種インターフェース仕様                           |    |

| J. | 4年1ファーフェースは19k                         |    |

|    |                                        |    |

|    | 5.2. CON1(シリアルインターフェース 1)              |    |

|    | 5.3. CON2(シリアルインターフェース 2)              |    |

|    | 5.4. CON3(USB インターフェース)                | 17 |

|    | 5.5. CON4(パラレルインターフェース)                |    |

|    | 5.6. CON5(パラレルインターフェース)                | 18 |

|    | 5.7. CON6(EP9315 JTAG)                 |    |

|    | 5.8. CON7                              |    |

|    | 5.9. CON8(同期シリアル/AC97/I2S)             |    |

|    | 5.10. CON9(IDE インターフェース)               |    |

|    | 5.11. CON10(コンパクトフラッシュ)                |    |

|    | 5.12. CON11(LAN コネクタ)                  |    |

|    |                                        |    |

|    | 5.13. CON12(VGA コネクタ)                  |    |

|    | 5.14. CON13(電源入力コネクタ)                  |    |

|    | 5.15. CCON14(拡張電源入力)                   |    |

|    | 5.16. J1, J2(PC/104 準拠拡張バス)            |    |

|    | 5.16.1. PC/104 拡張バスアクセス時の注意事項          | 27 |

|    | 5.16.2. アクセスタイミング                      | 28 |

|    | 5.17. LED (D4)                         | 29 |

|    | 5.18. LED (D5, D6)                     |    |

|    | 5.19. LED (D14)                        |    |

|    | 5.20. JP1, JP2                         |    |

|    | 5.20.1. JP1(ブート ROM の選択)               |    |

|    |                                        |    |

|    | 5.20.2. JP2(ブート Linux の選択)             | 31 |

|    | 5.21. コネクタ/スイッチ型式                      | 32 |

|    | 5.22. LED 型式(参考)                       |    |

| 6. | その他の各種機能                               | 34 |

|    | 6.1. CPLD 内部レジスタ(I/O Control Register) | 34 |

|    | 6.1.1. I/O Control レジスタのメモリマップ         |    |

|    | 6.1.2. 各種 I/O Control レジスタの詳細          |    |

|    | 6.1.3. PC/104 の割り込みコントローラの仕組み          |    |

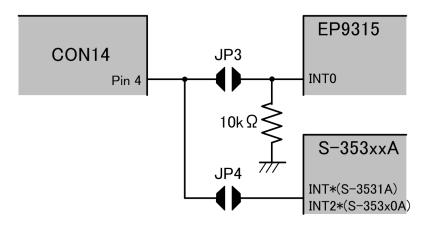

|    | 6.2. 外部割込みについて                         |    |

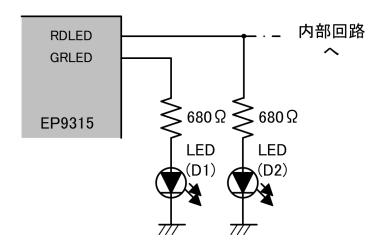

|    | 6.3. LED(D1, D2)                       |    |

|    | 0.9. LLD(D1, D2)                       | 31 |

|    | 6.3.1. 基板リビジョン E 以前の LED(D2)仕様 | 37 |

|----|--------------------------------|----|

|    | 6.3.2. 基板リビジョン E 以後の LED(D2)仕様 |    |

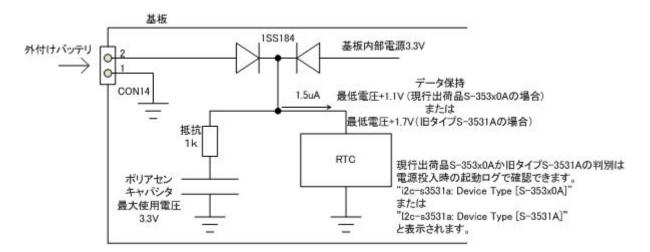

|    | 6.4. カレンダ時計(Real Time Clock)   |    |

|    | 6.5. 電源回路の構成                   | 39 |

| 7. | 基板形状図                          | 40 |

|    | 7.1. ANO10 基板形状図               | 41 |

|    | 7.2 ANO11 基板形状図                | 42 |

# 図目次

| 3.1. Armadillo-9 ブロック図                | . 12 |

|---------------------------------------|------|

| 5.1. 各種インターフェースの配置                    | . 15 |

| 5.2. PC/104 バスのメモリ空間                  | . 27 |

| 5.3. PC/104 バスへのアクセス方法                | . 28 |

| 5.4. PC/104 バスアクセスタイミング               | . 29 |

| 5.5. LED(D4)の接続                       | . 30 |

| 5.6. LED(D5,6)の接続<br>5.7. LED(D14)の接続 | . 30 |

| 5.7. LED(D14)の接続                      | . 31 |

| 5.8. ジャンパコネクタ                         | . 32 |

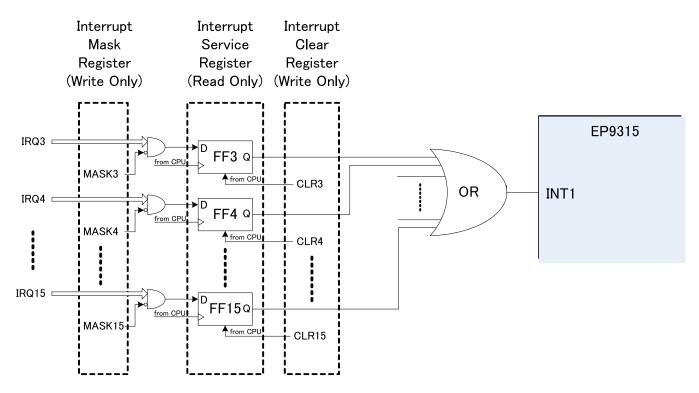

| 6.1. PC/104 の割り込みコントローラの仕組み           | . 36 |

| 6.2. EXTIRQ の接続                       | . 37 |

| 6.3. LED(D1,D2)の接続(基板リビジョン E 以前)      | . 38 |

| 6.4. LED(D1,D2)の接続(基板リビジョン E 以後)      | . 38 |

| 6.5. 外付けバッテリーの接続                      | . 39 |

| 6.6. Armadillo-9 の電源回路構成              | . 39 |

| 7.1. ANO10 の基板形状                      | . 41 |

| 7.2. ANO11 の基板形状                      | . 42 |

# 表目次

| 3.1. Armadillo-9 ボード仕様              | 11 |

|-------------------------------------|----|

| 4.1. Armadillo-9 物理メモリマップ           | 13 |

| 4.2. Armadillo-9 Linux 使用時の論理メモリマップ | 14 |

| 5.1. 各種インターフェースの内容                  | 15 |

| 5.2. CON1 信号配列                      | 16 |

| 5.3. CON2 信号配列                      | 17 |

| 5.4. CON3 信号配列                      | 17 |

| 5.5. CON4 信号配列                      | 18 |

| 5.6. パラレルインターフェースの電気的仕様             | 18 |

| 5.7. CON5 信号配列                      |    |

| 5.8. CON8 信号配列                      |    |

| 5.9. 各モードにおけるピンの機能                  | 20 |

| 5.10. CON9 信号配列                     |    |

| 5.11. CON10 信号配列                    | 21 |

| 5.12. CON11 信号配列                    | 22 |

| 5.13. CON12 信号配列                    | 23 |

| 5.14. 解像度と水平周波数                     | 23 |

| 5.15. CON13 信号配列                    | 23 |

| 5.16. CON14 信号配列                    | 24 |

| 5.17. J1 信号配列(1)                    | 24 |

| 5.18. J1 信号配列(2)                    | 25 |

| 5.19. J2 信号配列(1)                    | 26 |

| 5.20. J2 信号配列(2)                    | 26 |

| 5.21. LED(D5,D6) の状態                | 30 |

| 5.22. LED(D14) の状態                  | 30 |

| 5.23. ジャンパの設定と動作                    |    |

| 5.24. コネクタ/スイッチ型式の一覧                | 32 |

| 5.25. LED 型式の例                      | 33 |

| 6.1. I/O Control レジスタのメモリマップ        |    |

| 6.2. 各種 I/O Control レジスタの詳細         |    |

| 6.3. 各種 I/O Control レジスタの各ビットの意味    |    |

|                                     |    |

|                                     |    |

# 1. はじめに

## 1.1. 本書および関連ファイルのバージョンについて

本書を含めた関連マニュアル、ソースファイルやイメージファイルなどの関連ファイルは最新版を使用することをおすすめいたします。本書を読み進める前に、Armadillo サイト(http://armadillo.atmarktechno.com)から最新版の情報をご確認ください。

## 1.2. 本書の構成

本マニュアルは、Armadillo シリーズを使用する上で必要な情報のうち、以下の点について記載されています。

- ハードウェア概要

- ・メモリマップ

- インターフェース仕様

- ・ 基板の形状

- ・ケースの形状(Armadillo-2x0のみ)

- ・LCD パネル仕様(Armadillo-500 FX インターフェースボードのみ)

Armadillo シリーズの機能を最大限に引き出すために、ご活用いただければ幸いです。

# 2. 注意事項

### 2.1. 安全に関する注意事項

本製品を安全にご使用いただくために、特に以下の点にご注意ください。

- · ご使用の前に必ず製品マニュアルおよび関連資料をお読みになり、使用上の注意を守って正しく安全にお使いください。

- ・マニュアルに記載されていない操作・拡張などを行う場合は、弊社 Web サイトに掲載されている資料やその他技術情報を十分に理解した上で、お客様自身の責任で安全にお使いください。

- ・水・湿気・ほこり・油煙等の多い場所に設置しないでください。火 災、故障、感電などの原因になる場合があります。

- ・本製品に搭載されている部品の一部は、発熱により高温になる場合があります。周囲温度や取扱いによってはやけどの原因となる恐れがあります。本体の電源が入っている間、または電源切断後本体の温度が下がるまでの間は、基板上の電子部品、及びその周辺部分には触れないでください。

- ・本製品を使用して、お客様の仕様による機器・システムを開発される場合は、製品マニュアルおよび関連資料、弊社 Web サイトで提供している技術情報のほか、関連するデバイスのデータシート等を熟読し、十分に理解した上で設計・開発を行ってください。また、信頼性および安全性を確保・維持するため、事前に十分な試験を実施してください。

- ・本製品は、機能・精度において極めて高い信頼性・安全性が必要とされる用途(医療機器、交通関連機器、燃焼制御、安全装置等)での使用を意図しておりません。これらの設備や機器またはシステム等に使用された場合において、人身事故、火災、損害等が発生した場合、当社はいかなる責任も負いかねます。

- ・本製品には、一般電子機器用(OA機器・通信機器・計測機器・工作機械等)に製造された半導体部品を使用しています。外来ノイズやサージ等により誤作動や故障が発生する可能性があります。万一誤作動または故障などが発生した場合に備え、生命・身体・財産等が侵害されることのないよう、装置としての安全設計(リミットスイッチやヒューズ・ブレーカー等の保護回路の設置、装置の多重化等)に万全を期し、信頼性および安全性維持のための十分な措置を講じた上でお使いください。

- ・無線 LAN 機能を搭載した製品は、心臓ペースメーカーや補聴器などの医療機器、火災報知器や自動ドアなどの自動制御器、電子レンジ、高度な電子機器やテレビ・ラジオに近接する場所、移動体識別用の構

内無線局および特定小電力無線局の近くで使用しないでください。製品が発生する電波によりこれらの機器の誤作動を招く恐れがあります。

### 2.2. 取扱い上の注意事項

本製品に恒久的なダメージをあたえないよう、取扱い時には以下のような点にご注意ください。

本製品 本製品について**改造**を行った場合は**保証対象外**となりますので十分ご注意ください。また、 の改造 改造やコネクタ等の増設<sup>[1]</sup>を行う場合は、作業前に必ず動作確認を行うようお願いします。

電源の 本製品や周辺回路に電源が入っている状態での汎用入出力コネクタの着脱は、絶対に行わ投入 ないでください。

静電気 本製品には CMOS デバイスを使用していますので、ご使用になる時までは、帯電防止対策 のされている、出荷時のパッケージ等にて保管してください。

ラッチ 電源および入出力からの過大なノイズやサージ、電源電圧の急激な変動等により、使用しアップ ている CMOS デバイスがラッチアップを起こす可能性があります。いったんラッチアップ 状態となると、電源を切断しないかぎりこの状態が維持されるため、デバイスの破損につ ながることがあります。ノイズの影響を受けやすい入出力ラインには、保護回路を入れることや、ノイズ源となる装置と共通の電源を使用しない等の対策をとることをお勧めします。

衝撃 落下や衝撃などの強い振動を与えないでください。

### 2.3. ソフトウェア使用に関しての注意事項

本製品に含まれるソフト ウェアについて 本製品に含まれるソフトウェア(付属のドキュメント等も含みます)は、現状有姿(AS IS)にて提供いたします。お客様ご自身の責任において、使用用途・目的の適合について、事前に十分な検討と試験を実施した上でお使いください。当社は、当該ソフトウェアが特定の目的に適合すること、ソフトウェアの信頼性および正確性、ソフトウェアを含む本製品の使用による結果について、お客様に対しなんら保証も行うものではありません。

### 2.4. 保証について

本製品の本体基板は、製品に添付もしくは弊社 Web サイトに記載している「製品保証規定」に従い、ご購入から 1 年間の交換保証を行っています。添付品およびソフトウエアは保証対象外となりますのでご注意ください。

製品保証規定 http://www.atmark-techno.com/support/warranty-policy

### 2.5. 輸出について

本製品の開発・製造は、原則として日本国内での使用を想定して実施しています。本製品を輸出する際は、輸出者の責任において、輸出関連法令等を遵守し、必要な手続きを行ってください。海外の法令および規則への適合については当社はなんらの保証を行うものではありません。本製品および関連技術は、大量破壊兵器の開発目的、軍事利用その他軍事用途の目的、その他国内外の法令および規則により製造・使用・販売・調達が禁止されている機器には使用することができません。

<sup>[1]</sup>コネクタを増設する際にはマスキングを行い、周囲の部品に半田くず、半田ボール等付着しないよう十分にご注意ください。

## 2.6. 商標について

・Armadillo は株式会社アットマークテクノの登録商標です。その他の記載の商品名および会社名は、 各社・各団体の商標または登録商標です。™、®マークは省略しています。

・SD、SDHC、microSD、microSDHC、SDIO ロゴは SD-3C、LLC の商標です。

# 3. 概要

# 3.1. ボード概要

Armadillo-9 の主な仕様を表 3-1 に示します。

#### 表 3.1 Armadillo-9 ボード仕様

| プロセッサ        | CirrusLogic EP9315-CB                             |  |  |

|--------------|---------------------------------------------------|--|--|

|              | ARM920T コア採用                                      |  |  |

|              | · ARM9TDMI CPU                                    |  |  |

|              | <ul><li>16kB 命令キャッシュ</li></ul>                    |  |  |

|              | ・16kB データキャッシュ                                    |  |  |

|              | ・Thumb code(16bit 命令セット)サポート                      |  |  |

| システムクロック     | CPU Core クロック: 200MHz                             |  |  |

|              | BUS クロック: 100MHz                                  |  |  |

| メモリ          | SDRAM: 64MB(32bit 幅)                              |  |  |

|              | FLASH: 8MB(16bit 幅)                               |  |  |

| LAN インターフェース | 10BASE-T/100BASE-TX                               |  |  |

| シリアルインターフェース | 2 チャンネル(調歩同期, Max: 230.4kbps)                     |  |  |

|              | RS232C レベル入出力                                     |  |  |

|              | フロー制御                                             |  |  |

|              | ・シリアルインターフェース 1:フロー制御ピン有り(CTS,RTS,DTR,DSR,DCD,RI) |  |  |

|              | ・シリアルインターフェース 2:フロー制御ピン無し                         |  |  |

| 汎用パラレル入出力    | 8ビット+4ビット                                         |  |  |

| タイマ          | ・16 ビット汎用タイマ:2 チャンネル                              |  |  |

|              | (1 チャンネルは Linux のシステムタイマに使用)                      |  |  |

|              | ・32 ビット汎用タイマ:1 チャンネル                              |  |  |

|              | ・ 40 ビットデバッグ向けタイマ:1 チャンネル                         |  |  |

| VGA          | コネクタ形状: ミニ D-Sub15 ピン                             |  |  |

|              | 最大解像度 1024×768                                    |  |  |

|              | · 1024×768(8bit Color)                            |  |  |

|              | 800×600(8/16bit Color)                            |  |  |

|              | · 640×480(8/16bit Color)                          |  |  |

| USB (Host)   | 2.0 Full Speed (12Mbps) 1 チャンネル, Type-A コネクタ      |  |  |

| ストレージ        | IDE I/F(2.0mm ピッチ 44 ピン)                          |  |  |

|              | PIO モード、ATA33 モード対応                               |  |  |

| カレンダ時計       | SII 社製:S-3531A (または S-35380A、S-35390A)            |  |  |

|              | ポリアセンキャパシタによりバックアップ                               |  |  |

|              | (ボード外部の電池併用可能)                                    |  |  |

| コンパクトフラッシュ   | Type I/II に対応 (I/O, メモリカード対応)                     |  |  |

| 拡張バス         | PC/104 準拠ピン配列(16bit)                              |  |  |

| 基板サイズ        | 90.2 × 95.9 (突起部含まず)                              |  |  |

| 電源電圧         | 5V±5%                                             |  |  |

| 消費電流/電力      | 400mA(Typ.)/2W(Typ.)                              |  |  |

| 使用温度範囲       | 0°C~+60°C                                         |  |  |

| 耐振動性         | JIS C 0040(IEC-68-2-6)により測定                       |  |  |

|              | 水平、垂直ともに、2G 10Hz~500Hz まで対応                       |  |  |

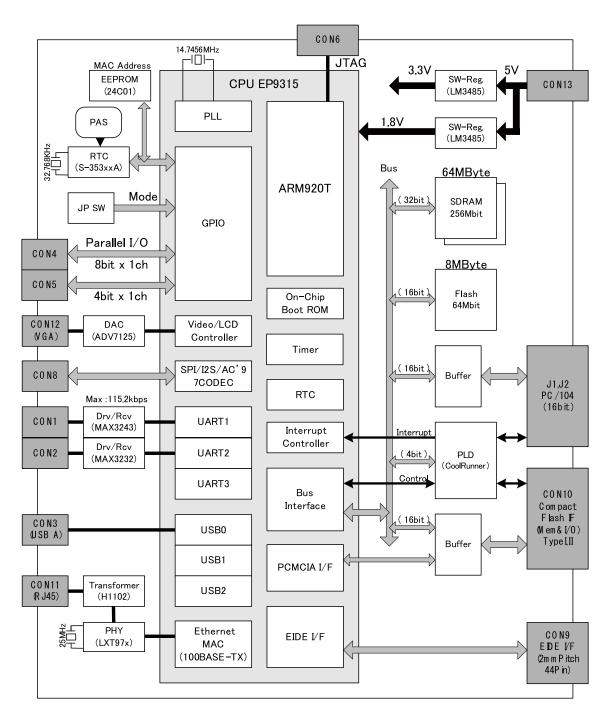

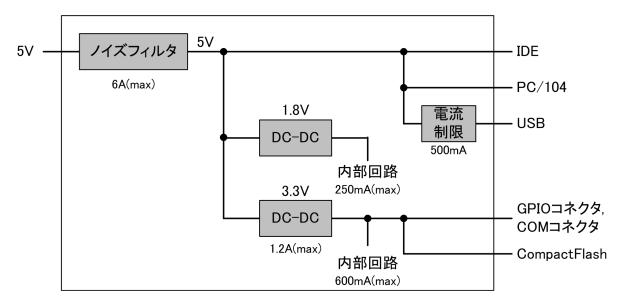

# 3.2. ブロック図

Armadillo-9 のブロック図を図 3-1 に示します。

Armadillo-9 ハードウェアマニュアル 概要

図 3.1 Armadillo-9 ブロック図

# 4. メモリマップ

## 4.1. 物理メモリマップ

Armadillo-9 の物理メモリマップは次の通りです。

表 4.1 Armadillo-9 物理メモリマップ

| Start Address              | End Address                | デバイス                        | メモリエリア        | 設定      |

|----------------------------|----------------------------|-----------------------------|---------------|---------|

| 0x0000 0000                | 0x0FFF FFFF                | Reserved                    | CS0           |         |

| 0x1000 0000                | 0x1000 000F                | I/O Control Register        | CS1           | 8bit 幅  |

| 0x1000 0010                | 0x11FF FFFF                | Reserved                    |               |         |

| 0x1200 0000                | 0x1200 FFFF                | PC/104 I/O 空間               |               |         |

|                            |                            | (8bit)                      |               |         |

| 0x1201 0000                | 0x12FF FFFF                | Reserved                    |               |         |

| 0x1300 0000                | 0x13FF FFFF                | PC/104 Memory 空間            |               |         |

|                            |                            | (8bit)                      |               |         |

| 0x1400 0000                | 0x1FFF FFFF                | Reserved                    |               |         |

| 0x2000 0000                | 0x21FF FFFF                | Reserved                    | CS2           | 16bit 幅 |

| 0x2200 0000                | 0x2200 FFFF                | PC/104 I/O 空間               |               |         |

|                            |                            | (16bit)                     |               |         |

| 0x2201 0000                | 0x22FF FFFF                | Reserved                    |               |         |

| 0x2300 0000                | 0x23FF FFFF                | PC/104 Memory 空間            |               |         |

|                            |                            | (16bit)                     |               |         |

| 0x2400 0000                | 0x2FFF FFFF                | Reserved                    |               |         |

| 0x3000 0000                | 0x3FFF FFFF                | Reserved                    | CS3           |         |

| 0x4000 0000                | 0x47FF FFFF                | Compact Flash               | PCMCIA        | 16bit 幅 |

|                            |                            | (I/O 空間)                    |               |         |

| 0x4800 0000                | 0x4BFF FFFF                | Compact Flash               |               |         |

|                            |                            | (Attribute 空間)              |               |         |

| 0x4C00 0000                | 0x4FFF FFFF                | Compact Flash               |               |         |

| 0.5000.0000                | 0 5555 5555                | (Memory 空間)                 |               |         |

| 0x5000 0000                | 0x5FFF FFFF                | Reserved                    |               |         |

| 0x6000 0000                | 0x607F FFFF                | Flash Memory                | CS6           | 16bit 幅 |

| 0.0000.0000                | 0 0555 5555                | (8MB)                       |               |         |

| 0x6080 0000                | 0x6FFF FFFF                | Reserved                    | 007           |         |

| 0x7000 0000                | 0x7FFF FFFF                | Reserved                    | CS7           |         |

| 0x8000 0000                | 0x8008 FFFF                | EP9315 Internal Register    | CPU<br>System |         |

| 0.0000.0000                | 0.0000.0555                | (AHB)                       | Register      |         |

| 0x8009 0000                | 0x8009 3FFF                | Internal Boot ROM<br>(16kB) | rtegistei     |         |

| 0x8009 4000                | 0x8009 FFFF                | Reserved                    |               |         |

| 0x8009 4000<br>0x800A 0000 | 0x8009 FFFF<br>0x800F FFFF | EP9315 Internal Register    |               |         |

| UXOUUA UUUU                | UXOUUF FFFF                | (AHB)                       |               |         |

| 0x8010 0000                | 0x807F FFFF                | Reserved                    |               |         |

| 0x8080 0000                | 0x8094 FFFF                | EP9315 Internal Register    |               |         |

|                            |                            | (APB)                       |               |         |

| 0x8095 0000                | 0x8FFF FFFF                | Reserved                    |               |         |

| 0x9000 0000                | 0xBFFF FFFF                | Reserved                    |               |         |

| Start Address | End Address | デバイス     | メモリエリア  | 設定      |

|---------------|-------------|----------|---------|---------|

| 0xC000 0000   | 0xC1FF FFFF | SDRAM    | SDCE0   | 32bit 幅 |

|               |             | (32MB)   | (SDRAM) |         |

| 0xC200 0000   | 0xC3FF FFFF | Reserved |         |         |

| 0xC400 0000   | 0xC5FF FFFF | SDRAM    |         |         |

|               |             | (32MB)   |         |         |

| 0xC600 0000   | 0xCFFF FFFF | Reserved |         |         |

| 0xD000 0000   | 0xFFFF FFFF | Reserved |         |         |

# 4.2. Linux 使用時の論理メモリマップ

Linux を使用する場合、Armadillo-9 は MMU により次の論理メモリマップに設定されます。

表 4.2 Armadillo-9 Linux 使用時の論理メモリマップ

| Start Address | End Address  | デバイス                              | メモリエリア           | 設定      |

|---------------|--------------|-----------------------------------|------------------|---------|

| 動的に確保         | +0x007F FFFF | Flash Memory<br>(8MB)             | CS6              | 16bit 幅 |

| 0xC000 0000   | 0xC3FF FFFF  | SDRAM<br>(64MB)                   | SDCE0<br>(SDRAM) | 32bit 幅 |

| 0xC400 0000   | 0xCFFF FFFF  | Reserved                          |                  |         |

| 0xD000 0000   | 0xD7FF FFFF  | Compact Flash<br>(I/O 空間)         | PCMCIA           | 16bit 幅 |

| 0xD800 0000   | 0xDBFF FFFF  | Compact Flash<br>(Attribute 空間)   |                  |         |

| 0xDC00 0000   | 0xDFFF FFFF  | Compact Flash<br>(Memory 空間)      |                  |         |

| 0xF000 0000   | 0xF000 000F  | I/O Control Register              | CS1              | 8bit 幅  |

| 0xF000 0010   | 0xF1FF FFFF  | Reserved                          |                  |         |

| 0xF200 0000   | 0xF200 FFFF  | PC/104 I/O 空間<br>(8bit)           |                  |         |

| 0xF201 0000   | 0xF2FF FFFF  | Reserved                          |                  |         |

| 0xF300 0000   | 0xF3FF FFFF  | PC/104 Memory 空間<br>(8bit)        |                  |         |

| 0xF400 0000   | 0xF5FF FFFF  | Reserved                          |                  |         |

| 0xF600 0000   | 0xF600 FFFF  | PC/104 I/O 空間<br>(16bit)          | CS2              | 16bit 幅 |

| 0xF601 0000   | 0xF6FF FFFF  | Reserved                          |                  |         |

| 0xF700 0000   | 0xF7FF FFFF  | PC/104 Memory 空間<br>(16bit)       |                  |         |

| 0xF800 0000   | 0xFEFF FFFF  | Reserved                          |                  |         |

| 0xFF00 0000   | 0xFF08 FFFF  | EP9315 Internal Register<br>(AHB) | CPU<br>System    |         |

| 0xFF09 0000   | 0xFF09 3FFF  | Internal Boot ROM<br>(16kB)       | Register         |         |

| 0xFF09 4000   | 0xFF09 FFFF  | Reserved                          |                  |         |

| 0xFF0A 0000   | 0xFF0F FFFF  | EP9315 Internal Register (AHB)    |                  |         |

| 0xFF10 0000   | 0xFF7F FFFF  | Reserved                          |                  |         |

| 0xFF80 0000   | 0xFF94 FFFF  | EP9315 Internal Register (APB)    |                  |         |

| 0xFF95 0000   | 0xFFFF FFFF  | Reserved                          |                  |         |

# 5. 各種インターフェース仕様

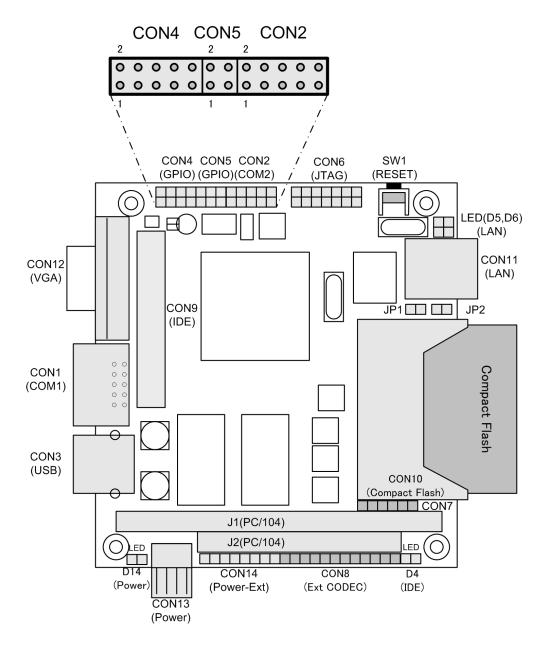

## 5.1. 各種インターフェースの配置

Armadillo-9 のインターフェースの配置は次の通りです。

図 5.1 各種インターフェースの配置

表 5.1 各種インターフェースの内容

| 部品番号 | インターフェース       | 備考 |

|------|----------------|----|

| CON1 | シリアルインターフェース 1 |    |

| 部品番号        | インターフェース                                 | 備考          |  |  |

|-------------|------------------------------------------|-------------|--|--|

| CON2        | CON2 シリアルインターフェース 2                      |             |  |  |

| CON3        | USB インターフェース                             | Type-A コネクタ |  |  |

|             | (Host, USB2.0, FullSpeed:12Mbps)         |             |  |  |

| CON4        | パラレルインターフェース(8bit 汎用入出力)                 | コネクタ非搭載     |  |  |

| CON5        | パラレルインターフェース(4bit 汎用入出力)                 | コネクタ非搭載     |  |  |

| CON6        | JTAG インターフェース                            | コネクタ非搭載     |  |  |

| CON7        | (Reserved)                               | コネクタ非搭載     |  |  |

| CON8        | 同期シリアル/AC97 CODEC/I2S CODEC              | コネクタ非搭載     |  |  |

| CON9        | IDE インターフェース(2.0mm ピッチ, 44 ピン)           |             |  |  |

| CON10       | コンパクトフラッシュ スロット(Type I/II, I/O/メモリカード対応) |             |  |  |

| CON11       | LAN コネクタ (10BASE-T/100BASE-TX)           | RJ-45       |  |  |

| CON12       | VGA インターフェース(D-Sub15 ピン)                 |             |  |  |

| CON13       | 電源入力端子(5V,12V)                           |             |  |  |

| CON14       | 拡張電源入力端子(-5V, -12V, RTC バックアップ)          | コネクタ非搭載     |  |  |

| J1, J2      | PC/104 拡張コネクタ(スタックスルー)                   | コネクタ非搭載     |  |  |

| LED (D4)    | IDE アクセス                                 | LED 非搭載     |  |  |

| LED (D5, 6) | LAN アクセス (Link, Active)                  |             |  |  |

| LED (D14)   | 電源                                       | LED 非搭載     |  |  |

| JP1, JP2    | 起動モード設定ジャンパ                              |             |  |  |

| SW1         | RESET スイッチ                               |             |  |  |

## 5.2. CON1(シリアルインターフェース 1)

CON1 は非同期(調歩同期)シリアルインターフェースです。CPU(EP9315)の UART1 と接続されています。

- ・信号入出力レベル:RS232C レベル

- ・最大データ転送レート:230.4kbps

- ・フロー制御:CTS, RTS, DTR, DSR, DCD, RI

- · FIFO:送受信ともに 16 バイト 内蔵

表 5.2 CON1 信号配列

| 番号 | 信号名   | I/O   | 機能                               |

|----|-------|-------|----------------------------------|

| 1  | DCD   | I     | EP9315 の EGPIO1 (Port A: 1)ピンに接続 |

| 2  | DSR   | I     | EP9315 内蔵の UART1-DSR ピンに接続       |

| 3  | RXD   | I     | EP9315 内蔵の UART1-RXD ピンに接続       |

| 4  | RTS   | 0     | EP9315 内蔵の UART1-RTS ピンに接続       |

| 5  | TXD   | 0     | EP9315 内蔵の UART1-TXD ピンに接続       |

| 6  | CTS   | I     | EP9315 内蔵の UART1-CTS ピンに接続       |

| 7  | DTR   | 0     | EP9315 内蔵の UART1-DTR ピンに接続       |

| 8  | RI    | I     | EP9315 の EGPIO0 (Port A:0)ピンに接続  |

| 9  | GND   | Power | 電源(GND)                          |

| 10 | +3.3V | Power | 電源(+3.3V) <sup>[1]</sup>         |

[1]電圧精度±5%

下記シリアル番号に該当する Armadillo-9 の CON1 同士を接続した場合、正常にデータ通信を行うことが出来ません。

これは、該当する Armadillo-9 で使用されている RS232C レベル変換 IC が互いにシャットダウンモードになってしまう為です。

#### · S/N: 040201-000000~040401-001994

上記シリアル番号以外の Armadillo-9 は IC を変更している為、問題が発生することはありません。

# 5.3. CON2(シリアルインターフェース 2)

CON2 は非同期(調歩同期)シリアルインターフェースです。CPU(EP9315)の UART2 と接続されています。

- ・信号入出力レベル:RS232C レベル

- ・最大データ転送レート:230.4kbps

- ・フロー制御:なし

- · FIFO:送受信ともに 16 バイト 内蔵

#### 表 5.3 CON2 信号配列

| 番号 | 信号名   | I/O   | 機能                         |

|----|-------|-------|----------------------------|

| 1  | -     |       |                            |

| 2  | -     |       |                            |

| 3  | RXD   | 1     | EP9315 内蔵の UART2-RXD ピンに接続 |

| 4  | RTS   | 0     | CON2(6 ピン)と基板上で接続(ループバック)  |

| 5  | TXD   | 0     | EP9315 内蔵の UART2-TXD ピンに接続 |

| 6  | CTS   | 1     | CON2(4 ピン)と基板上で接続(ループバック)  |

| 7  | -     |       |                            |

| 8  | -     |       |                            |

| 9  | GND   | Power | 電源(GND)                    |

| 10 | +3.3V | Power | 電源(+3.3V) <sup>[1]</sup>   |

<sup>[1]</sup>電圧精度±5%

## 5.4. CON3(USB インターフェース)

CON3 は USB シリアルインターフェースです。CPU(EP9315)上の USBO と接続されています。

- ・データ転送モード: USB2.0 Full Speed(12Mbps)、Low Speed(1.5Mbps)

- ・供給電源:電圧+5V 、電流 500mA(max)

- ・コネクタ形状:Type A

表 5.4 CON3 信号配列

| 番号 | 信号名  | 1/0   | 機能                      |

|----|------|-------|-------------------------|

| 1  | +5V  | Power | 電源(+5V, 最大 500mA の供給可能) |

| 2  | USB- | I/O   | USB のマイナス側信号            |

| 3  | USB+ | I/O   | USB のプラス側信号             |

| 4  | GND  | Power | 電源(GND)                 |

Armadillo サイト [http://armadillo.atmark-techno.com/]にて、動作確認済み USB デバイス情報を 随時更新していますのでご確認ください。

### 5.5. CON4(パラレルインターフェース)

CON4 は汎用入出力ポートです。CPU(EP9315)の GPIO(General Purposel/O)と接続されています。CPU 内の PADR(Port A data register I/O: 0x8084~0000~番地)、PADDR(Port A data direction register I/O: 0x8084~0010~番地)、PBDR(Port B data register I/O: 0x8084~0004~番地)、PBDDR(Port B data direction register I/O: 0x8084~0014~番地)を使用して制御することができます。なお、EP9315 の Port A: $0\sim3$ 、Port B: $4\sim7~$ については、内部回路で使用しているので、ユーザ側では使用できません。

表 5.5 CON4 信号配列

| 番号 | 信号名    | I/O   | 機能                                           |

|----|--------|-------|----------------------------------------------|

| 1  | GND    | Power | 電源(GND)                                      |

| 2  | +3.3V  | Power | 電源(+3.3V) <sup>[1]</sup>                     |

| 3  | GPIO_0 | I/O   | 汎用入出力ポート 0 (EP9315 の EGPIO4(Port A:4)ピンに接続)  |

| 4  | GPIO_1 | I/O   | 汎用入出力ポート 1 (EP9315 の EGPIO5(Port A:5)ピンに接続)  |

| 5  | GPIO_2 | I/O   | 汎用入出力ポート 2 (EP9315 の EGPIO6(Port A:6)ピンに接続)  |

| 6  | GPIO_3 | I/O   | 汎用入出力ポート 3 (EP9315 の EGPIO7(Port A:7)ピンに接続)  |

| 7  | GPIO_4 | I/O   | 汎用入出力ポート 4 (EP9315 の EGPIO8(Port B:0)ピンに接続)  |

| 8  | GPIO_5 | I/O   | 汎用入出力ポート 5 (EP9315 の EGPIO9(Port B:1)ピンに接続)  |

| 9  | GPIO_6 | I/O   | 汎用入出力ポート 6 (EP9315 の EGPIO10(Port B:2)ピンに接続) |

| 10 | GPIO_7 | I/O   | 汎用入出力ポート 7 (EP9315 の EGPIO11(Port B:3)ピンに接続) |

<sup>[1]</sup>電圧精度±5%

パラレルインターフェースの電気的仕様は次の通りです。

表 5.6 パラレルインターフェースの電気的仕様

| Symbol          | Parameter                 | Min                    | Max                    | Unit | Conditions                              |

|-----------------|---------------------------|------------------------|------------------------|------|-----------------------------------------|

| V <sub>IH</sub> | CMOS Input high voltage   | 0.65×V <sub>DDIO</sub> | V <sub>DDIO</sub> +0.3 | V    | V <sub>DDIO</sub> =3.3V                 |

| V <sub>IL</sub> | CMOS Input low voltage    | -0.3                   | 0.35×V <sub>DDIO</sub> | V    |                                         |

| V <sub>OH</sub> | CMOS Output high voltage  | 2.8                    |                        | V    | I <sub>OH</sub> =4mA                    |

| V <sub>OL</sub> | CMOS Output low voltage   |                        | 0.5                    | V    | I <sub>OL</sub> =-4mA                   |

| I <sub>OH</sub> | High level Output current |                        | 4                      | mA   |                                         |

| I <sub>OL</sub> | Low level Output current  |                        | -4                     | mA   |                                         |

| I IL            | Input leakage current     |                        | 10.0                   | μΑ   | V <sub>IN</sub> =V <sub>DD</sub> or GND |

### 5.6. CON5(パラレルインターフェース)

CON5 は汎用入出力ポートです。CPU(EP9315)の GPIO(General Purpose I/O)と接続されています。CPU 内の PDDR(Port D data register I/O:  $0x8084\ 000C$  番地)、PDDDR(Port D data direction register I/O:  $0x8084\ 001C$  番地)を使用して制御することができます。パラレルインターフェースの電気的仕様は表 5-6 の通りです。なお、EP9315 の Port D:0 $\sim$ 3 については、内部回路で使用しているので、ユーザ側では使用 できません。

| 表 5.7 | CON5 | 信号配列 |

|-------|------|------|

|-------|------|------|

| 番号 | 信号名       | I/O | 機能                                   |

|----|-----------|-----|--------------------------------------|

| 1  | GPIO_Ext0 | I/O | 汎用入出力ポート 0 (EP9315 の Port D:4 ピンに接続) |

| 2  | GPIO_Ext1 | I/O | 汎用入出力ポート 1 (EP9315 の Port D:5 ピンに接続) |

| 3  | GPIO_Ext2 | I/O | 汎用入出力ポート 2 (EP9315 の Port D:6 ピンに接続) |

| 4  | GPIO_Ext3 | I/O | 汎用入出力ポート 3 (EP9315 の Port D:7 ピンに接続) |

# 5.7. CON6(EP9315 JTAG)

CON6 は Armadillo-9 に JTAG デバッガを接続するためのコネクタです。CPU(EP9315)の JTAG 信号と接続されています。

| 番号 | 信号名   | I/O   | 機能                       |

|----|-------|-------|--------------------------|

| 1  | +3.3V | Power | 電源(+3.3V) <sup>[1]</sup> |

| 2  | GND   | Power | 電源(GND)                  |

| 3  | TRST* | I     | EP9315 の JTAG TRST*      |

| 4  | GND   | Power | 電源(GND)                  |

| 5  | TDI   | I     | EP9315のJTAG TDI          |

| 6  | GND   | Power | 電源(GND)                  |

| 7  | TMS   | I     | EP9315のJTAG TMS          |

| 8  | GND   | Power | 電源(GND)                  |

| 9  | TCK   | I     | EP9315のJTAG TCK          |

| 10 | GND   | Power | 電源(GND)                  |

| 11 | TDO   | 0     | EP9315のJTAG TDO          |

| 12 | -     |       | (Reserved)               |

| 13 | +3.3V | Power | 電源(+3.3V) <sup>[1]</sup> |

| 14 | GND   | Power | 電源(GND)                  |

<sup>[1]</sup>電圧精度±5%

### 5.8. CON7

このコネクタを使用する場合の動作は保証されておりません。

## 5.9. CON8(同期シリアル/AC97/I2S)

CON8 は同期シリアル、AC97CODEC、オーディオ CODEC のデバイスを接続するためのコネクタですが、このコネクタを使用する場合の動作は保証されておりません。以下にピン配列を示します。

表 5.8 CON8 信号配列

| 番号 | 信号名     | I/O   | 機能                       |

|----|---------|-------|--------------------------|

| 1  | GND     | Power | 電源(GND)                  |

| 2  | ASDI    | I     | 表 5-9 を参照(CPU:ASDI)      |

| 3  | ARST*   | 0     | 表 5-9 を参照(CPU:ARST*)     |

| 4  | ASDO    | 0     | 表 5-9 を参照(CPU:ASDO)      |

| 5  | ASYNC   | 0     | 表 5-9 を参照(CPU:ASYNC)     |

| 6  | ABITCLK | I     | 表 5-9 を参照(CPU:BITCLK)    |

| 7  | +3.3V   | Power | 電源(+3.3V) <sup>[1]</sup> |

| 8  | SSPRX1  |       | 表 5-9 を参照 (CPU:SSPRX1)   |

| 9  | SSPTX1  | 0     | 表 5-9 を参照 (CPU: SSPTX1)  |

| 10 | SFRM1   | 0     | 表 5-9 を参照 (CPU:SFRM1)    |

| 11 | SCLK1   | 0     | 表 5-9 を参照 (CPU:SCLK1)    |

| 12 | GND     | Power | 電源(GND)                  |

<sup>[1]</sup>電圧精度±5%

CON8 のピンに割り当てられる機能は、EP9315 のレジスタ設定によって切り替えることができます。「Normal Mode」、「I2S on AC97 Mode」、「I2S on SSP Mode」の3 つモードがあり、0x8093 0080 番地の DeviceCfg Register の「bit6:I2S on AC97」、「bit7:I 2S on SSP」を書き換えることでモード変更をすることができます。

| 表 5.9: | 各モー | ドにおける | ピンの機能 |

|--------|-----|-------|-------|

|--------|-----|-------|-------|

| ピン名     | Normal Mode        | I2S on SSP Mode    | I2S on AC97 Mode  |

|---------|--------------------|--------------------|-------------------|

| SSPRX1  | SPI Serial Input   | I2S Serial Input   | SPI Serial Input  |

| SSPTX1  | SPI Serial Output  | I2S Serial Output  | SPI Serial Output |

| SFRM1   | SPI Frame Clock    | I2S Frame Clock    | SPI Frame Clock   |

| SCLK1   | SPI Bit Clock      | I2S Serial Clock   | SPI Bit Clock     |

| ASDI    | AC97 Serial Input  | AC97 Serial Input  | I2S Serial Input  |

| ASDO    | AC97 Serial Output | AC97 Serial Output | I2S Serial Output |

| ASYNC   | AC97 Frame Clock   | AC97 Frame Clock   | I2S Frame Clock   |

| ABITCLK | AC97 Bit Clock     | AC97 Bit Clock     | I2S Serial Clock  |

| ARST*   | AC97 Reset         | AC97 Reset         | I2S Master Clock  |

## 5.10. CON9(IDE インターフェース)

CON9 は IDE のデバイスを接続するための 2mm ピッチ 44 ピンコネクタです。2.5 インチのハードディスクドライブとストレートのフラットケーブルで接続することができます。転送モードは PIO モードの他 に ATA33 に対応しています。以下にピン配列を示します。

表 5.10 CON9 信号配列

| 番号 | 信号名    | I/O   | 機能            |

|----|--------|-------|---------------|

| 1  | RESET* | 0     | リセット信号        |

| 2  | GND    | Power | 電源(GND)       |

| 3  | DD7    | I/O   | データバス(bit7)   |

| 4  | DD8    | I/O   | データバス(bit8)   |

| 5  | DD6    | I/O   | データバス(bit6)   |

| 6  | DD9    | I/O   | データバス(bit9)   |

| 7  | DD5    | I/O   | データバス(bit5)   |

| 8  | DD10   | I/O   | データバス(bit10)  |

| 9  | DD4    | I/O   | データバス(bit4)   |

| 10 | DD11   | I/O   | データバス(bit11)  |

| 11 | DD3    | I/O   | データバス(bit3)   |

| 12 | DD12   | I/O   | データバス(bit12)  |

| 13 | DD2    | I/O   | データバス(bit2)   |

| 14 | DD13   | I/O   | データバス(bit13)  |

| 15 | DD1    | I/O   | データバス(bit1)   |

| 16 | DD14   | I/O   | データバス(bit14)  |

| 17 | DD0    | I/O   | データバス(bit0)   |

| 18 | DD15   | I/O   | データバス(bit15)  |

| 19 | GND    | Power | 電源(GND)       |

| 20 | NC     | -     | 非サポート         |

| 21 | DMARQ  | I     | DMA リクエスト     |

| 22 | GND    | Power | 電源(GND)       |

| 23 | DIOW*  | 0     | I/O ライト・イネーブル |

| 24 | GND    | Power | 電源(GND)       |

| 25 | DIOR*  | 0     | I/O リード・イネーブル |

| 26 | GND    | Power | 電源(GND)       |

| 27 | IORDY  | I     | IO レディ        |

| 28 | CSEL   | 0     | ケーブルセレクト(GND) |

| 番号 | 信号名    | I/O   | 機能           |

|----|--------|-------|--------------|

| 29 | DMACK* | 0     | DMA アクノリッジ   |

| 30 | GND    | Power | 電源(GND)      |

| 31 | INTRQ  | I     | 割り込みリクエスト    |

| 32 | NC     | -     | 非サポート        |

| 33 | DA1    | 0     | アドレスバス(bit1) |

| 34 | NC     | -     | 非サポート        |

| 35 | DA0    | 0     | アドレスバス(bit0) |

| 36 | DA2    | 0     | アドレスバス(bit2) |

| 37 | CS0*   | 0     | チップセレクト 0    |

| 38 | CS1*   | 0     | チップセレクト 1    |

| 39 | DASP*  | I     | デバイスアクセス     |

| 40 | GND    | Power | 電源(GND)      |

| 41 | +5V    | Power | 電源(+5V)      |

| 42 | +5V    | Power | 電源(+5V)      |

| 43 | GND    | Power | 電源(GND)      |

| 44 | NC     | -     | 非サポート        |

# 5.11. CON10(コンパクトフラッシュ)

CON10 はコンパクトフラッシュ のインターフェースです。I/O モード、メモリモードに対応しており、ATA デ バイスや I/O カードを接続することができます。

- ・接続モード:I/O モード、メモリモード

- · 対応形状:Type I、Type II

- ・3.3V カード専用、活線挿抜(ホットプラグ)対応

#### 表 5.11 CON10 信号配列

| 番号 | 信号名   | I/O   | 機能                       |

|----|-------|-------|--------------------------|

| 1  | GND   | Power | 電源(GND)                  |

| 2  | D3    | I/O   | データバス(bit3)              |

| 3  | D4    | I/O   | データバス(bit4)              |

| 4  | D5    | I/O   | データバス(bit5)              |

| 5  | D6    | I/O   | データバス(bit6)              |

| 6  | D7    | I/O   | データバス(bit7)              |

| 7  | CE1*  | 0     | カードイネーブル信号 1             |

| 8  | A10   | 0     | アドレスバス(bit10)            |

| 9  | OE*   | 0     | データアウトイネーブル              |

| 10 | A9    | 0     | アドレスバス(bit9)             |

| 11 | A8    | 0     | アドレスバス(bit8)             |

| 12 | A7    | 0     | アドレスバス(bit7)             |

| 13 | +3.3V | Power | 電源(+3.3V) <sup>[1]</sup> |

| 14 | A6    | 0     | アドレスバス(bit6)             |

| 15 | A5    | 0     | アドレスバス(bit5)             |

| 16 | A4    | 0     | アドレスバス(bit4)             |

| 17 | A3    | 0     | アドレスバス(bit3)             |

| 18 | A2    | 0     | アドレスバス(bit2)             |

| 19 | A1    | 0     | アドレスバス(bit1)             |

| 20 | A0    | 0     | アドレスバス(bit0)             |

| 21 | D0    | I/O   | データバス(bit0)              |

| 22 | D1    | I/O   | データバス(bit1)              |

| 23 | D2    | I/O   | データバス(bit2)              |

| 番号 | 信号名     | I/O   | 機能                       |

|----|---------|-------|--------------------------|

| 24 | IOCS16* | I     | I/O 16bit                |

| 25 | CD2*    | I     | カード検出                    |

| 26 | CD1*    | I     | カード検出                    |

| 27 | D11     | I/O   | データバス(bit11)             |

| 28 | D12     | I/O   | データバス(bit12)             |

| 29 | D13     | I/O   | データバス(bit13)             |

| 30 | D14     | I/O   | データバス(bit14)             |

| 31 | D15     | I/O   | データバス(bit15)             |

| 32 | CE2*    | 0     | カードイネーブル信号 2             |

| 33 | VS1*    |       |                          |

| 34 | IORD*   | 0     | I/O リード・イネーブル            |

| 35 | IOWR*   | 0     | I/O ライト・イネーブル            |

| 36 | WE*     | 0     | ライトイネーブル                 |

| 37 | IREQ    | I     | 割り込み要求                   |

| 38 | +3.3V   | Power | 電源(+3.3V) <sup>[1]</sup> |

| 39 | -       | -     |                          |

| 40 | VS2*    |       |                          |

| 41 | RESET*  | 0     | リセット                     |

| 42 | WAIT*   | I     | ウエイト                     |

| 43 | -       | -     |                          |

| 44 | REG*    | 0     | レジスタセレクト, I/O イネーブル      |

| 45 | BVD2    | I     |                          |

| 46 | BVD1    | I     |                          |

| 47 | D8      | I/O   | データバス(bit8)              |

| 48 | D9      | I/O   | データバス(bit9)              |

| 49 | D10     | I/O   | データバス(bit10)             |

| 50 | GND     | Power | 電源(GND)                  |

<sup>[1]</sup>電圧精度±5%

Armadillo サイト [http://armadillo.atmark-techno.com/]にて、動作確認済みコンパクトフラッシュを随時更新していますのでご確認ください。

## 5.12. CON11(LAN コネクタ)

CON11 は 10BASE-T/100BASE-TX の LAN インターフェースです。カテゴリ 5 以上の Ethernet ケーブルを接続することができます。通常はハブに対してストレートケーブルで接続しますが、クロスケーブルを使用して直接パソコン等の機器と接続することもできます。搭載している PHY チップ(LXT97x)の割り込み出力信号(MDINT\*)は未接続(開放)となっています。

#### 表 5.12 CON11 信号配列

| 番号 | 信号名 | I/O | 機能               |

|----|-----|-----|------------------|

| 1  | TX+ | 0   | 差動のツイストペア送信出力(+) |

| 2  | TX- | 0   | 差動のツイストペア送信出力(-) |

| 3  | RX+ | I   | 差動のツイストペア受信入力(+) |

| 4  | -   | -   |                  |

| 5  | -   | -   |                  |

| 6  | RX- | I   | 差動のツイストペア受信入力(-) |

| 番号 | 信号名 | 1/0 | 機能 |

|----|-----|-----|----|

| 7  | -   | -   |    |

| 8  | -   | -   |    |

## 5.13. CON12(VGA コネクタ)

CON12 は汎用のディスプレイを接続する為の VGA コネクタ(ミニ D-Sub15 ピン)です。汎用の CRT、液晶ディスプレイを接続することができます。

#### 表 5.13 CON12 信号配列

| 番号 | 信号名    | I/O   | 機能          |

|----|--------|-------|-------------|

| 1  | RED    | 0     | アナログ 色信号(赤) |

| 2  | GREEN  | 0     | アナログ 色信号(緑) |

| 3  | BLUE   | 0     | アナログ 色信号(青) |

| 4  | -      | -     |             |

| 5  | GND    | Power | 信号接地(GND)   |

| 6  | GND    | Power | 信号接地(GND)   |

| 7  | GND    | Power | 信号接地(GND)   |

| 8  | GND    | Power | 信号接地(GND)   |

| 9  | -      | -     |             |

| 10 | GND    | Power | 信号接地(GND)   |

| 11 | -      | -     |             |

| 12 | -      | -     |             |

| 13 | H_SYNC | 0     | 水平同期信号      |

| 14 | V_SYNC | 0     | 垂直同期信号      |

| 15 | -      | 1     |             |

#### 表 5.14 解像度と水平周波数

| 解像度      | 色数      | 水平周波数(垂直周波数)  |

|----------|---------|---------------|

| 640×480  | 8/16bit | 31.5kHz(60Hz) |

| 800×600  | 8/16bit | 37.9kHz(60Hz) |

| 1024×768 | 8bit    | 48.4kHz(60Hz) |

## 5.14. CON13(電源入力コネクタ)

Armadillo-9 に供給する電源接続コネクタです。Armadillo-9 の動作に必要な最低限の電源は+5V-GNDです。+12V は PC/104 の+12V 供給ピンにそのまま接続されます。

#### 表 5.15 CON13 信号配列

| 番号 | 信号名          | 1/0                             | 機能                        |  |

|----|--------------|---------------------------------|---------------------------|--|

| 1  | 1 +5V Power  | Dower                           | 電源(+5V)入力                 |  |

| '  |              | PC/104 の+5V、 IDE の+5V ピンに供給されます |                           |  |

| 2  | GND          | Power                           | 電源(GND)                   |  |

| 3  | GND          | Power                           | 電源(GND)                   |  |

| 4  | 4 +12V Power |                                 | 電源(+12V)入力 <sup>[1]</sup> |  |

| 4  | +12V         | Power                           | PC/104 の+12V ピンに供給されます。   |  |

\_\_\_\_\_\_ <sup>[1]</sup> Armadillo-9 の動作には必要ありません。

# 5.15. CCON14(拡張電源入力)

Armadillo-9 に供給する電源接続コネクタです。

| 表 5.16 | S CONT | 4 信号配列 |

|--------|--------|--------|

|--------|--------|--------|

| 番号 | 信号名    | I/O   | 機能                                                                                                                                                  |

|----|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | GND    | Power | 電源(GND)                                                                                                                                             |

| 2  | BAT    | Power | RTC(S-353xxA)バックアップ用電源入力 <sup>[1]</sup>                                                                                                             |

| 3  | GND    | Power | 電源(GND)                                                                                                                                             |

| 4  | EXTIRQ | I/O   | JP3 をショートしている場合:<br>CPU(EP9315)の割込み入力信号(INTO)に接続<br>JP4 をショートしている場合:<br>RTC(S-353xxA)の割込み出力信号に接続<br>(S-3531A は INT*、S-35380A または S-35390A では INT2*) |

| 5  | GND    | Power | 電源(GND)                                                                                                                                             |

| 6  | -5V    | Power | 電源(-5V)入力 <sup>[1]</sup><br>PC/104 の-5V ピンに供給                                                                                                       |

| 7  | GND    | Power | 電源(GND)                                                                                                                                             |

| 8  | -12V   | Power | 電源(-12V)入力 <sup>[1]</sup><br>PC/104 の-12V ピンに供給                                                                                                     |

<sup>[1]</sup> Armadillo-9 の動作には必要ありません。

## 5.16. J1, J2(PC/104 準拠拡張バス)

J1, J2 は PC/104 準拠のバス配列を採用した拡張バスです $^{[1]}$ 。64kB の I/O エリアと 16Mbyte のメモリエリアを持っています。しかし ARM アーキテクチャは x86 系 CPU のような I/O エリア(I/O 専用のアクセス)を持たないため、通常のメモリ空間に I/O エリアを配置しています。

また、この拡張バスは PC/104 規格のサブセットです。通常の PC/104 バスとの主な違いは次の通りです。

- ・ダイナミックバスサイジングを非サポート

- ・DMA(DREQ/DACK)を非サポート

- 外部マスタを非サポート

- バスアクセスサイクルが固定

表 5.17 J1 信号配列(1)

| ピン番号 | 信号名      | I/O | 機能                                                 |

|------|----------|-----|----------------------------------------------------|

| A1   | IOCHCHK* | (I) | 非サポート (未接続) <sup>[1]</sup>                         |

| A2   | D7       | I/O | データバス(bit7)                                        |

| A3   | D6       | I/O | データバス(bit6)                                        |

| A4   | D5       | I/O | データバス(bit5)                                        |

| A5   | D4       | I/O | データバス(bit4)                                        |

| A6   | D3       | I/O | データバス(bit3)                                        |

| A7   | D2       | I/O | データバス(bit2)                                        |

| A8   | D1       | I/O | データバス(bit1)                                        |

| A9   | D0       | I/O | データバス(bit0)                                        |

| A10  | IOCHRDY* | I   | 低速デバイスに合わせてアクセスサイクル延長<br>(5V プルアップ) <sup>[1]</sup> |

| A11  | AEN      | 0   | バス開放(GND)                                          |

| A12  | A19      | 0   | アドレスバス(bit19)                                      |

| A13  | A18      | 0   | アドレスバス(bit18)                                      |

| A14  | A17      | 0   | アドレスバス(bit17)                                      |

<sup>[1]</sup>各信号は TTL レベルです。(VOH:2.4V 以上,VOL:0.4V 以下,VIH:2V 以上,VIL:0.8V 以下)

| ピン番号 | 信号名 | I/O   | 機能            |

|------|-----|-------|---------------|

| A15  | A16 | 0     | アドレスバス(bit16) |

| A16  | A15 | 0     | アドレスバス(bit15) |

| A17  | A14 | 0     | アドレスバス(bit14) |

| A18  | A13 | 0     | アドレスバス(bit13) |

| A19  | A12 | 0     | アドレスバス(bit12) |

| A20  | A11 | 0     | アドレスバス(bit11) |

| A21  | A10 | 0     | アドレスバス(bit10) |

| A22  | A9  | 0     | アドレスバス(bit9)  |

| A23  | A8  | 0     | アドレスバス(bit8)  |

| A24  | A7  | 0     | アドレスバス(bit7)  |

| A25  | A6  | 0     | アドレスバス(bit6)  |

| A26  | A5  | 0     | アドレスバス(bit5)  |

| A27  | A4  | 0     | アドレスバス(bit4)  |

| A28  | A3  | 0     | アドレスバス(bit3)  |

| A29  | A2  | 0     | アドレスバス(bit2)  |

| A30  | A1  | 0     | アドレスバス(bit1)  |

| A31  | A0  | 0     | アドレスバス(bit0)  |

| A32  | GND | Power | 電源(GND)       |

[1]プルアップやプルダウンで論理を固定していたり、未接続であることを括弧内の表示で示しています。論理を固定している場合、すべて Armadillo-9 の基板上に搭載された抵抗でおこなっています。

### 表 5.18 J1 信号配列(2)

| ピン番号 | 信号名       | I/O   | 機能                                   |

|------|-----------|-------|--------------------------------------|

| B1   | GND       | Power | 電源(GND)                              |

| B2   | RESET_DRV | 0     | リセット出力                               |

| B3   | +5V       | Power | 電源(+5V)                              |

| B4   | IRQ9      | I     | 割り込みリクエスト 9(5V プルアップ) <sup>[1]</sup> |

| B5   | -5V       | Power | 電源(-5V)                              |

| В6   | DRQ2      | (I)   | 非サポート(未接続)[1]                        |

| B7   | -12V      | Power | 電源(-12V)                             |

| B8   | ENDXFR*   | (I)   | 非サポート(5V プルアップ) <sup>[1]</sup>       |

| В9   | +12V      | Power | 電源(+12V)                             |

| B10  | (KEY)     | -     | GND                                  |

| B11  | SMEMW*    | 0     | メモリ・ライト・ストローブ                        |

| B12  | SMEMR*    | 0     | メモリ・リード・ストローブ                        |

| B13  | IOW*      | 0     | 1/0 ライト・ストローブ                        |

| B14  | IOR*      | 0     | I/O リード・ストローブ                        |

| B15  | DACK3*    | (O)   | 非サポート(3.3V プルアップ) <sup>[1]</sup>     |

| B16  | DRQ3      | (I)   | 非サポート(未接続)[1]                        |

| B17  | DACK1*    | (O)   | 非サポート(3.3V プルアップ) <sup>[1]</sup>     |

| B18  | DRQ1      | (I)   | 非サポート(未接続)[1]                        |

| B19  | REFRESH*  | (O)   | 非サポート(3.3V プルアップ) <sup>[1]</sup>     |

| B20  | SYSCLK    | 0     | 8.333MHz(CPU バスクロックの 1/12)           |

| B21  | IRQ7      | I     | 割り込みリクエスト 7(5V プルアップ) <sup>[1]</sup> |

| B22  | IRQ6      | I     | 割り込みリクエスト 6(5V プルアップ) <sup>[1]</sup> |

| B23  | IRQ5      | I     | 割り込みリクエスト 5(5V プルアップ) <sup>[1]</sup> |

| B24  | IRQ4      | I     | 割り込みリクエスト 4(5V プルアップ) <sup>[1]</sup> |

| B25  | IRQ3      | I     | 割り込みリクエスト 3(5V プルアップ) <sup>[1]</sup> |

| B26  | DACK2*    | (O)   | 非サポート(3.3V プルアップ) <sup>[1]</sup>     |

| B27  | T/C       | (O)   | 非サポート(3.3V プルアップ) <sup>[1]</sup>     |

| B28  | BALE      | 0     | アドレス・ラッチ・イネーブル                       |

| B29  | +5V       | Power | 電源(+5V)                              |

| B30  | OSC       | (O)   | 非サポート(未接続) <sup>[1]</sup>            |

| ピン番号 | 信号名 | 1/0   | 機能      |

|------|-----|-------|---------|

| B31  | GND | Power | 電源(GND) |

| B32  | GND | Power | 電源(GND) |

<sup>[1]</sup>プルアップやプルダウンで論理を固定していたり、未接続であることを括弧内の表示で示しています。論理を固定している場合、すべて Armadillo-9 の基板上に搭載された抵抗でおこなっています。

#### 表 5.19 J2 信号配列(1)

| ピン番号 | 信号名   | I/O   | 機能                       |

|------|-------|-------|--------------------------|

| CO   | GND   | Power | 電源(GND)                  |

| C1   | SBHE* | 0     | バス・ハイ・イネーブル              |

| Ci   | SDITE |       | (データバス上位 8bit 使用時にアクティブ) |

| C2   | A23   | 0     | アドレスバス(23bit)            |

| C3   | A22   | 0     | アドレスバス(22bit)            |

| C4   | A21   | 0     | アドレスバス(21bit)            |

| C5   | A20   | 0     | アドレスバス(20bit)            |

| C6   | A19   | 0     | アドレスバス(19bit)            |

| C7   | A18   | 0     | アドレスバス(18bit)            |

| C8   | A17   | 0     | アドレスバス(17bit)            |

| C9   | MEMR* | 0     | メモリ・リード・ストローブ            |

| C10  | MEMW* | 0     | メモリ・ライト・ストローブ            |

| C11  | D8    | I/O   | データバス(bit8)              |

| C12  | D9    | I/O   | データバス(bit9)              |

| C13  | D10   | I/O   | データバス(bit10)             |

| C14  | D11   | I/O   | データバス(bit11)             |

| C15  | D12   | I/O   | データバス(bit12)             |

| C16  | D13   | I/O   | データバス(bit13)             |

| C17  | D14   | I/O   | データバス(bit14)             |

| C18  | D15   | I/O   | データバス(bit15)             |

| C19  | (KEY) | -     | GND                      |

#### 表 5.20 J2 信号配列(2)

| ピン番号 | 信号名      | I/O   | 機能                                    |

|------|----------|-------|---------------------------------------|

| D0   | GND      | Power | 電源(GND)                               |

| D1   | MEMCS16* | (I)   | 非サポート(5V プルアップ) <sup>[1]</sup>        |

| D2   | IOCS16*  | (I)   | 非サポート(5V プルアップ) <sup>[1]</sup>        |

| D3   | IRQ10    | I     | 割り込みリクエスト 10(5V プルアップ) <sup>[1]</sup> |

| D4   | IRQ11    | I     | 割り込みリクエスト 11(5V プルアップ) <sup>[1]</sup> |

| D5   | IRQ12    | I     | 割り込みリクエスト 12(5V プルアップ) <sup>[1]</sup> |

| D6   | IRQ15    | I     | 割り込みリクエスト 15(5V プルアップ) <sup>[1]</sup> |

| D7   | IRQ14    | I     | 割り込みリクエスト 14(5V プルアップ) <sup>[1]</sup> |

| D8   | DACK0*   | (O)   | 非サポート(3.3V プルアップ) <sup>[1]</sup>      |

| D9   | DREQ0    | (I)   | 非サポート                                 |

| D10  | DACK5*   | (O)   | 非サポート(3.3V プルアップ) <sup>[1]</sup>      |

| D11  | DREQ5    | (I)   | 非サポート                                 |

| D12  | DACK6*   | (O)   | 非サポート(3.3V プルアップ) <sup>[1]</sup>      |

| D13  | DREQ6    | (I)   | 非サポート                                 |

| D14  | DACK7*   | (O)   | 非サポート(3.3V プルアップ) <sup>[1]</sup>      |

| D15  | DREQ7    | (I)   | 非サポート                                 |

| D16  | +5V      | Power | 電源(+5V)                               |

| D17  | MASTER*  | (I)   | 非サポート(5V プルアップ) <sup>[1]</sup>        |

| D18  | GND      | Power | 電源(GND)                               |

| D19  | GND      | Power | 電源(GND)                               |

<sup>[1]</sup>プルアップやプルダウンで論理を固定していたり、未接続であることを括弧内の表示で示しています。論理を固定している場合、すべて Armadillo-9 の基板上に搭載された抵抗でおこなっています。

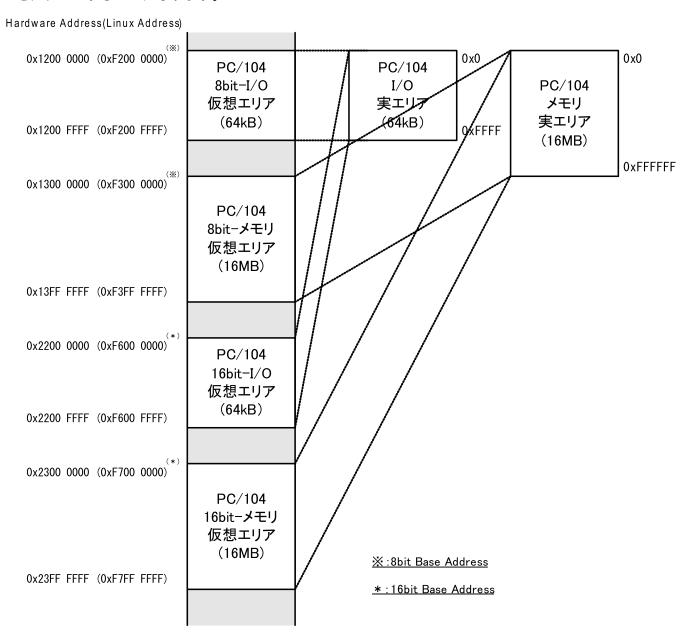

### 5.16.1. PC/104 拡張バスアクセス時の注意事項

Armadillo-9 の PC/104 拡張バスはダイナミックバスサイジング機能を備えていないため、PC/104 の I/O エリアまたはメモリエリアにアクセスする際には注意が必要です。Armadillo-9 は 1 つの I/O 実 エリア(64kB)とメモリ実エリア(16MB)を持っています。I/O、メモリのそれぞれの実エリアには 2 つの 仮想エリア(8bit,16bit)からアクセスすることができます。どちらの仮想エリアを使っても同じ実エリアをアクセスすることになります。

図 5.2 PC/104 バスのメモリ空間

それぞれの仮想エリアの使い分けは次のとおりです。

| 8bit 仮想エリア  | ・データバス(D7~D0)を使用して 8bit アクセスをする          |

|-------------|------------------------------------------|

|             | ・データバス(D15~D8)を使用して奇数アドレス番地に 8bit アクセスする |

| 16bit 仮想エリア | ・データバス(D7~D0)を使用して偶数アドレス番地に 8bit アクセスする  |

|             | ・データバス(D15~D0)を使用して 16bit アクセスする         |

#### 実エリアのアクセスには

・8(16)bit Base Address + 実工リアの offset Address でアクセスすることができます。

#### 8bit実エリアにアクセス 8bit仮想エリア D7 D0 +0x0 8bit Base Address +0x1 +0x2 +0x3 +0x4 +0x5: 実エリア +0x0 +0x1 16bit実エリアに8bit単位でアクセス +0x2 16bit仮想エリア +0x3 D15 D8D7 D0 +0x4+0x1 +0x0+0x5 16bit Base Address +0x6 +0x3+0x2 +0x5 +0x4 +0x716bit実エリアに16bit単位でアクセス 16bit仮想エリア D8D7 D15 D0 +0x0 16bit Base Address +0x2 +0x4

図 5.3 PC/104 バスへのアクセス方法

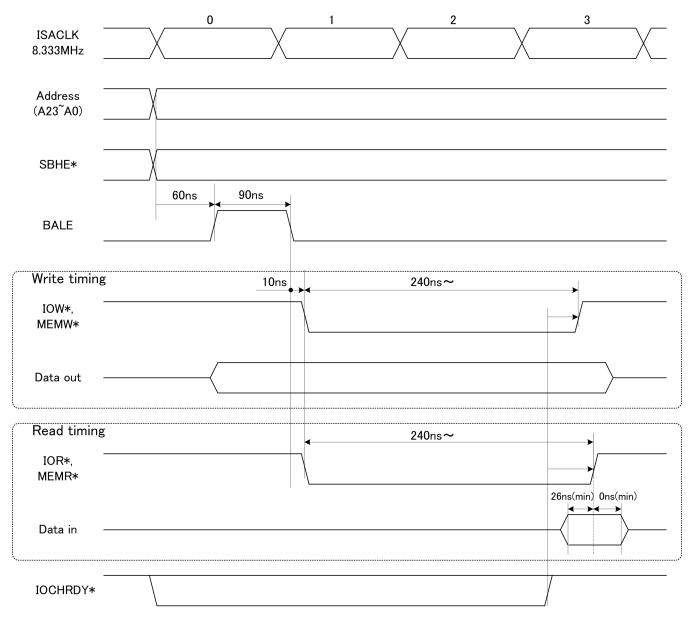

### 5.16.2. アクセスタイミング

PC/104 拡張バスへのアクセスタイミングは次の通りです。16bit アクセスした場合も 8bit アクセスした 場合もタイミングは同じです。

図 5.4 PC/104 バスアクセスタイミング

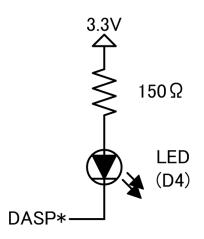

# 5.17. LED (D4)

LED(D4)は IDE のアクセスランプです

図 5.5 LED(D4)の接続

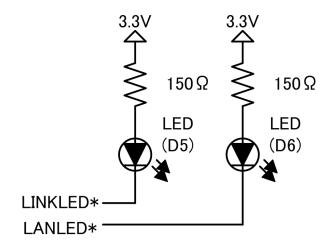

# 5.18. LED (D5, D6)

LED(D5,6)は LAN の状態を表しています。

表 5.21 LED(D5,D6) の状態

| 部品番号 | 名称   | 点灯                                                    | 消灯                                             |

|------|------|-------------------------------------------------------|------------------------------------------------|

| D5   | LINK | LAN ケーブルが接続されており、10BASE-T または 100BASE-TX のリンクが確立されている | LAN ケーブルが接続されていないか、接続している相手の状態が Active な状態ではない |

| D6   | LAN  | データ送受信時                                               | 非データ送受信時                                       |

図 5.6 LED(D5,6)の接続

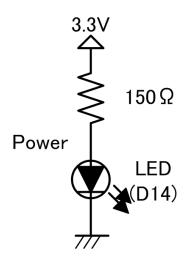

# 5.19. LED (D14)

LED(D14)は Armadillo-9 の電源状態を表しています。

表 5.22 LED(D14) の状態

| 部品番号 | 名称    | 点灯                    | 消灯                     |  |  |

|------|-------|-----------------------|------------------------|--|--|

| D14  | Power | Armadillo-9 の電源が入っている | Armadillo-9 の電源が入っていない |  |  |

図 5.7 LED(D14)の接続

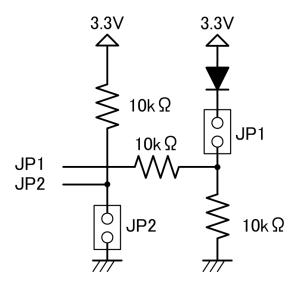

### 5.20. JP1, JP2

JP1,JP2 は Armadillo-9 の起動モードの設定を行います。

### 5.20.1. JP1(ブート ROM の選択)

ブートする際に使用するデバイスを、「オンボードフラッシュメモリ」または「オンチップブート ROM」から選択することができます。オンチップブート ROM はシリアルインターフェース 1 からプログラムをダウンロードしてから実行し、オンボードフラッシュメモリを書き換えるとき等に使用します。オンチップブート ROM の詳細については、「EP9315 User's Guide」をご参照ください。

### 5.20.2. JP2(ブート Linux の選択)

Linux カーネルが格納されているデバイスを選択することができます。ただしこの JP の設定は Linux を搭載しているときのみ有効です。

#### 表 5.23 ジャンパの設定と動作

| JP1 | JP2                    | ブートデバイス                                                           | ブートカーネル                                                 |

|-----|------------------------|-------------------------------------------------------------------|---------------------------------------------------------|

| OFF | OFF                    | オンボードフラッ<br>シュメモリ                                                 | オンボードフラッシュメモリの Linux カーネル                               |

|     |                        |                                                                   | 1. IDE デバイスが搭載されている場合<br>IDE デバイスの Linux カーネルがブート       |

|     |                        | +  +*   \* ¬ =                                                    | 2. コンパクトフラッシュ が搭載されている場合<br>コンパクトフラッシュ の Linux カーネルがブート |

| OFF | ・ ON オンボードフラッ<br>シュメモリ | 3. IDE デバイスもコンパクトフラッシュも搭載されていない場合<br>ブートローダ「Hermit」がブート           |                                                         |

|     |                        | 4. IDE デバイスにもコンパクトフラッシュにも Linux カーネルを見つけられない場合 ブートローダ「Hermit」がブート |                                                         |

| ON  | -                      | オンチップブート<br>ROM                                                   | オンチップブート ROM のプログラムがブート                                 |

図 5.8 ジャンパコネクタ

# 5.21. コネクタ/スイッチ型式

CON1~14、J1~2、SW1 の型式等を表 5-24 に示します。

| 部品番号  | メーカ                  | 型式                      | 備考                |

|-------|----------------------|-------------------------|-------------------|

| CON1  | ヒロセ電機                | HIF3F-10PA-2.54DS       | 逆挿入防止形ボックス        |

| CON2  | -                    | 2×5 (2.54mm ピッチ)        | (非搭載)             |

| CON3  | 日本圧着端子               | UBA-4R-S14-2            | USB コネクタ(Type A)  |

| CON4  | -                    | 2×5 (2.54mm ピッチ)        | (非搭載)             |

| CON5  | -                    | 2×2 (2.54mm ピッチ)        | (非搭載)             |

| CON6  | -                    | 2×7 (2.54mm ピッチ)        | (非搭載)             |

| CON7  | -                    | 1×6 (2.54mm ピッチ)        | (非搭載)             |

| CON8  | -                    | 1×12 (2.54mm ピッチ)       | (非搭載)             |

| CON9  | ヒロセ電機                | A3A-44PA-2SV            | 44 ピン(2.0mm ピッチ)  |

| CON10 | 第一電子工業               | MCD-CEN750PC            | コンパクトフラッシュコネクタ    |

| CONTO | 另一电丁 <u>工</u> 来      | WCD-CEN750FC            | (Type I, II)      |

| CON11 | Full Rise Electronic | E5388-F00214            | RJ-45 コネクタ        |

| CON12 | 日本圧着端子               | KSEY-15S-3B6L19-13      | ミニ D-Sub15 ピンコネクタ |

| CON13 | Tyco Electronics     | 171826-4                | 4 ピン(2.5mm ピッチ)   |

| CON14 | -                    | 1×8 (2.54mm ピッチ)        | (非搭載)             |

| Jl    | Astron               | AT-ES1-64-12-2-GF       | PC/104 J1 スタックスルー |

| JI    | ASHOH                | A1-E31-04-12-2-GF       | (非搭載)             |

| J2    | Astron               | AT-ES1-20-12-1-GF(2 個)  | PC/104 J2 スタックスルー |

| JL    | ASHOH                | A1-L31-20-12-1-G1 (2 回) | (非搭載)             |

| SW1   | アルプス電気               | SKHHI MA010             | タクトスイッチ           |

表 5.24 コネクタ/スイッチ型式の一覧

# 5.22. LED 型式(参考)

Armadillo-9 に接続できる LED の型式等の例を表 5-25 に示します。

### 表 5.25 LED 型式の例

| 部品番号  | メーカ      | 型式            | 備考          |

|-------|----------|---------------|-------------|

| D4    | 東芝       | TLR123 等      | Red         |

| D5, 6 | Dialight | 553-0112-200等 | Red / Green |

| D14   | 東芝       | TLG123A 等     | Green       |

# 6. その他の各種機能

## 6.1. CPLD 内部レジスタ(I/O Control Register)

### 6.1.1. I/O Control レジスタのメモリマップ

Armadillo-9 の CPLD には PC/104 の I/O を制御するための I/O Control レジスタがあります。I/O Control レジスタのメモリマップは次の通りです。

表 6.1 I/O Control レジスタのメモリマップ

| Hardware Address | Linux Address | Read                        | Write                     |

|------------------|---------------|-----------------------------|---------------------------|

| 0x1000 0000      | 0xF000 0000   | Interrupt Service Register0 | Interrupt Clear Register0 |

| 0x1000 0001      | 0xF000 0001   | (Reserved)                  | (Reserved)                |

| 0x1000 0002      | 0xF000 0002   | Interrupt Service Register1 | Interrupt Clear Register1 |

| 0x1000 0003      | 0xF000 0003   | (Reserved)                  | (Reserved)                |

| 0x1000 0004      | 0xF000 0004   | Interrupt Service Register2 | Interrupt Clear Register2 |

| 0x1000 0005      | 0xF000 0005   | (Reserved)                  | (Reserved)                |

| 0x1000 0006      | 0xF000 0006   | (Reserved)                  | (Reserved)                |

| 0x1000 0007      | 0xF000 0007   | (Reserved)                  | (Reserved)                |

| 0x1000 0008      | 0xF000 0008   | (Reserved)                  | Interrupt Mask Register0  |

| 0x1000 0009      | 0xF000 0009   | (Reserved)                  | (Reserved)                |

| 0x1000 000A      | 0xF000 000A   | (Reserved)                  | Interrupt Mask Register1  |

| 0x1000 000B      | 0xF000 000B   | (Reserved)                  | (Reserved)                |

| 0x1000 000C      | 0xF000 000C   | (Reserved)                  | Interrupt Mask Register2  |

| 0x1000 000D      | 0xF000 000D   | (Reserved)                  | (Reserved)                |

| 0x1000 000E      | 0xF000 000E   | (Reserved)                  | ISA mode Control Register |

| 0x1000 000F      | 0xF000 000F   | (Reserved)                  | (Reserved)                |

Interrupt Service Register(割 入ってきた割り込みの要因を見るレジスタです。 り込みサービスレジスタ)

Interrupt Clear Register(割り 割り込みサービスレジスタに入ってきた割り込み要因をクリアする 込み要因クリアレジスタ) レジスタです。

Interrupt Mask Register(割り 各種割り込みの入力を禁止(マスク)するレジスタです。 込みマスクレジスタ)

ISA mode Control Register PC/104(ISA) の転送モード及びリセットを設定するレジスタです。

### 6.1.2. 各種 I/O Control レジスタの詳細

各種 I/O Control レジスタの詳細は次のとおりです。

表 6.2 各種 I/O Control レジスタの詳細

| Register                          | Hardware       | Linux          |   |   |   |   | Da | ta    |       |       |

|-----------------------------------|----------------|----------------|---|---|---|---|----|-------|-------|-------|

| Name                              | Address        | Address        | 7 | 6 | 5 | 4 | 3  | 2     | 1     | 0     |

| Read Only                         |                |                |   |   |   |   |    |       |       |       |

| Interrupt<br>Service<br>Register0 | 0x1000<br>0000 | 0xF000<br>0000 | - | - | - | - | -  | IRQ15 | IRQ14 | IRQ12 |

| Register                           | Hardware       | Linux          |   |   |   |   | Da    | ta           |             |       |

|------------------------------------|----------------|----------------|---|---|---|---|-------|--------------|-------------|-------|

| Name                               | Address        | Address        | 7 | 6 | 5 | 4 | 3     | 2            | 1           | 0     |

| Interrupt<br>Service<br>Register 1 | 0x1000<br>0002 | 0xF000<br>0002 | - | - | ı | ı | IRQ11 | IRQ10        | IRQ9        | IRQ7  |

| Interrupt<br>Service<br>Register2  | 0x1000<br>0004 | 0xF000<br>0004 | - | - | - | - | IRQ6  | IRQ5         | IRQ4        | IRQ3  |

| Write Only                         |                |                |   |   |   |   |       |              |             |       |

| Interrupt<br>Clear<br>Register0    | 0x1000<br>0000 | 0xF000<br>0000 | - | - | - | - | -     | IRQ15        | IRQ14       | IRQ12 |

| Interrupt<br>Clear<br>Register1    | 0x1000<br>0002 | 0xF000<br>0002 | - | - | - | - | IRQ11 | IRQ10        | IRQ9        | IRQ7  |

| Interrupt<br>Clear<br>Register2    | 0x1000<br>0004 | 0xF000<br>0004 | - | - | - | - | IRQ6  | IRQ5         | IRQ4        | IRQ3  |

| Interrupt<br>Mask<br>Register0     | 0x1000<br>0008 | 0xF000<br>0008 | - | - | - | - | -     | IRQ15        | IRQ14       | IRQ12 |

| Interrupt<br>Mask<br>Register I    | 0x1000<br>000A | 0xF000<br>000A | - | - | - | ı | IRQ11 | IRQ10        | IRQ9        | IRQ7  |

| Interrupt<br>Mask<br>Register2     | 0x1000<br>000C | 0xF000<br>000C | - | - | ı | ı | IRQ6  | IRQ5         | IRQ4        | IRQ3  |

| ISA mode<br>Control<br>Register    | 0x1000<br>000E | 0xF000<br>000E | - | - | - | - | -     | ISA<br>reset | ISA<br>mode | -     |

#### 表 6.3 各種 I/O Control レジスタの各ビットの意味

| Register name             |                | Value | Description                     |

|---------------------------|----------------|-------|---------------------------------|

| Interrupt Service Regis   | tor            | 1     | IRQx 割込みが発生している                 |

| Interrupt Service Regis   | lei            | 0     | IRQx 割込みが発生していない                |

| Interrupt Clear Registe   | or.            | 1     | IRQx 割込みの要因をクリアする               |

| Interrupt Clear Registe   | 51             | 0     | IRQx 割込みの要因をクリアしない              |

| Interrupt Mask Registe    | ar             | 1     | IRQx 割込みの入力をマスクする               |

| Interrupt Mask Registe    | <del>2</del> 1 | 0     | IRQx 割込みの入力をマスクしない              |

|                           | ISA mode       | 1     | 高速(ISA 非互換)モード <sup>[1]</sup>   |

| ICA made Control Degister | ISA Mode       | 0     | ISA 互換モード                       |

| ISA mode Control Register | ISA reset      | 1     | PC/104 Bus の RESET 信号を ON( H )  |

|                           | ISA reset      | 1     | PC/104 Bus の RESET 信号を OFF( L ) |

<sup>[1]</sup> このモードを設定したときの動作は保証されておりません。

### 6.1.3. PC/104 の割り込みコントローラの仕組み

PC/104 の割り込みコントローラは CPLD(XCR3064) に組み込まれています。この割り込みコントローラ に接続されている割り込みの種類は IRQ3, 4, 5, 6, 7, 9, 10,11,12, 14, 15 です。割り込みコントローラの概念図は次のとおりです。

図 6.1 PC/104 の割り込みコントローラの仕組み

IMR ICR **ISR IRQx** CLK **MASKx CLRx FF**x 0 0 0 0 rise 1 1 edge 0 1 0

表 6.4 割り込み 真理値表[]]

[1] \* : Don't Care

IRQx は、アクティブハイ信号です。PC/104 から入力される IRQx は IMR(Interrupt Mask Register) によりマスク処理されます。マスクビットが"0"の場合、割り込み入力はそのまま通過し次段の FF に入力されます。マスクビットが"1"の場合割り込み入力がマスクされ、次段の FF には"0"が入力されます。

マスク処理を通過した割り込み入力信号は次段の ISR(Interrupt Service Register)を構成しているFF(フリップフロップ)で値を保持されます。

ISR に保持されている値は、ICR(Interrupt Clear Register)の対応するビットに"1"が入力されるまで値が保持されます。

ISR に保持されているすべての値の OR をとって、CPU(EP9315)の INT1 として割り込みが通知されます。INT1 は、アクティブハイ信号です。

### 6.2. 外部割込みについて

ボード外部から CON14 を通して CPU(EP9315)の割込み入力端子や RTC(S-353xxA)の割込み出力端子に 接続することができます。

CON14 の 4 番ピンと CPU(EP9315)の割込み入力端子(INTO)を接続する場合は JP3 をショートします。 CPU(EP9315)の INTO 端子は、CMOS3.3V の電圧レベル入力です。

CON14 の 4 番ピンと RTC(S-353xxA)の割込み出力端子を接続する場合は JP4 をショートします。 RTC(S-353xxA)の割込み端子は、Nch オープンドレイン出力です。(S-3531A は INT\*端子、S-35380A ま たは S-35390A では INT2\*端子に接続されます。)

工場出荷状態では、JP3.4 はオープンになっています。

図 6.2 EXTIRQ の接続

RTC(S-353xxA)の割込み端子はオープンドレイン出力のため、使用する場合には外付けにプルアップ抵抗が必要となります。また、端子には電源側の保護ダイオードが付いていないため、プルアップ抵抗の電源は必ず、Armadillo-9の+3.3Vを使用してください。

### 6.3. LED(D1, D2)

LED(D1)は CPU(EP9315)の PEO/GRLED ピンに接続された LED です。内蔵 ROM 起動時にステータス LED として機能した後、EP9315 の GPIO Port E を設定することにより、LED(D1)を制御することができます。LED(D2)は基板リビジョン $^{[1]}$ により仕様が変わります。

### 6.3.1. 基板リビジョン E 以前の LED(D2)仕様

LED(D2)は CPU(EP9315)の PE1/RDLED ピンに接続された LED ですが、この LED の信号は内部回路で使用していますので、設定を変更しないでください。

<sup>[1]</sup>基板リビジョンは基板半田面側に記載しています。記載例:[Rev.E]

図 6.3 LED(D1,D2)の接続(基板リビジョン E 以前)

### 6.3.2. 基板リビジョン E 以後の LED(D2)仕様

LED(D2)は CPU(EP9315)の GPIO Port C:7 ピンに接続された LED です。EP9315 の GPIO Port C を設定することにより、LED(D2)を制御することができます。

図 6.4 LED(D1,D2)の接続(基板リビジョン E 以後)

## 6.4. カレンダ時計(Real Time Clock)

カレンダ時計(Real Time Clock: S-3531A またはその互換品)は CPU(EP9315)と 2 線式シリアル (GPIO) で接続されています。CPU 側はパラレルポート B(PB4,5:EGPIO12,EGPIO13)をシリアルのように制御す ることにより、RTC へのアクセスを実現しています。

RTC はポリアセンキャパシタ(PAS)のバックアップにより電源切断時も一定時間の間動作することができます。長時間電源を切っている間も、RTC の内容を保持したい場合は、別途外付けのバッテリーを接続することができます。(データ保持電圧範囲 1.7~3.3V、消費電流 0.7uA Typ.)

図 6.5 外付けバッテリーの接続

RTC の保持に使用しているポリアセンキャパシタは温度によって寿命/充放電回数が著しく異なります。また、ポリアセンキャパシタは交換不可です。そのため、RTC バックアップが重要なシステムにおいては、別途バックアップ用電池をご使用下さい。バックアップ用電池をご利用になる場合、電圧は 3.3V を越えないように設計してください。

### 6.5. 電源回路の構成

Armadillo-9 内の電源回路の構成は図 6-5 の通りです。各制限の電流容量を超えないように、外部機器の接続、供給電源の設計を行ってください。

図 6.6 Armadillo-9 の電源回路構成

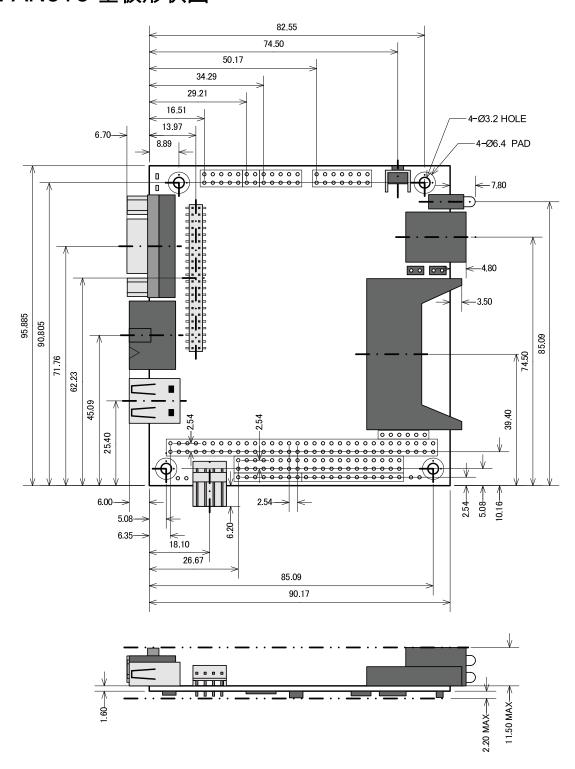

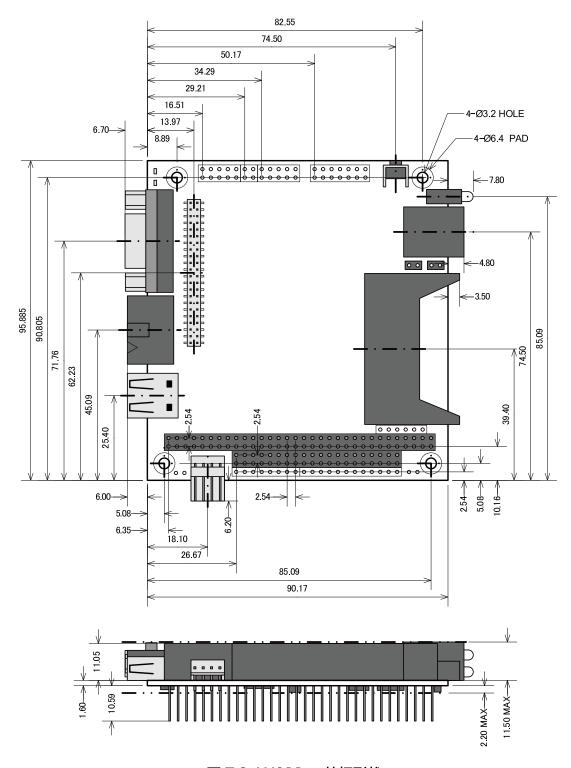

# 7. 基板形状図

型番 AN010 は PC/104 バスのコネクタが実装されていないもの、型番 AN011 は PC/104 バスのコネクタが実装されたものです。コネクタの実装以外機能の違いはありません。

# 7.1. ANO10 基板形状図

図 7.1 ANO10 の基板形状

# 7.2. ANO11 基板形状図

図 7.2 ANO11 の基板形状

### 改訂履歴

| バージョン | 年月日        | 改訂内容                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0.0 | 2004.12.18 | · 初版発行                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.0.1 | 2005.2.10  | <ul> <li>「表 3.1. Armadillo-9 ボード仕様」の GPIO の数を修正</li> <li>「表 4.1. Armadillo-9 物理メモリマップ」の SDRAM のメモリマップを修正</li> <li>「6.2. 外部割込みについて」 の記述を修正</li> <li>ドキュメント内の誤植を修正</li> </ul>                                                                                                                                                                                                                                                         |

| 1.0.2 | 2005.2.21  | <ul> <li>・「表 5.2. CON1 信号配列」 の記述を修正</li> <li>・「表 5.7. CON5 信号配列」 の記述を修正</li> <li>・「5.7. CON6(EP9315 JTAG)」 について、表中の記述を修正</li> <li>・「表 5.11. CON10 信号配列」 の記述を修正</li> <li>・ドキュメント内の誤植を修正</li> </ul>                                                                                                                                                                                                                                   |

| 1.0.3 | 2005.4.18  | <ul> <li>「5.2. CON1(シリアルインターフェース 1)」 について記述追加</li> <li>「5.4. CON3(USB インターフェース)」 について記述追加</li> <li>「5.11. CON10(コンパクトフラッシュ)」 について記述追加</li> <li>「図 5.4. PC/104 バスアクセスタイミング」 のリードタイミングの記述追加</li> <li>「表 5.24. コネクタ/スイッチ型式の一覧」 の記述を変更</li> <li>「図 7.1. AN010 の基板形状」 の寸法線を修正</li> <li>ドキュメント内の誤植を修正</li> </ul>                                                                                                                          |

| 1.0.4 | 2005.7.5   | <ul> <li>「表 3.1. Armadillo-9 ボード仕様」 に消費電力、使用温度範囲、耐振動性を追加</li> <li>「5.5. CON4(パラレルインターフェース)」 について記述追加</li> <li>「5.6. CON5(パラレルインターフェース)」 について記述追加</li> <li>「6.3. LED(D1, D2)」 に D2 の説明を追加</li> </ul>                                                                                                                                                                                                                                 |

| 1.0.5 | 2005.10.11 | ・「表 5.16. CON14 信号配列」 の EXTIRQ の記述を修正     ・「6.1.3. PC/104 の割り込みコントローラの仕組み」について記述<br>追加     ・「6.2. 外部割込みについて」 の記述追加     ・ドキュメント内の誤植を修正                                                                                                                                                                                                                                                                                               |

| 1.0.6 | 2006.1.25  | ・「表 5.9. 各モードにおけるピンの機能」 の記述を修正<br>・「6.4. カレンダ時計(Real Time Clock)」 について記述追加                                                                                                                                                                                                                                                                                                                                                          |

| 1.0.7 | 2007.7.20  | <ul> <li>ドキュメントプロパティのタイトルと作成者を修正</li> <li>「表 3.1. Armadillo-9 ボード仕様」の使用温度範囲を修正</li> <li>「表 3.1. Armadillo-9 ボード仕様」、「5.2. CON1(シリアルインターフェース 1)」、「5.3. CON2(シリアルインターフェース 2)」の最大ボーレートを修正</li> <li>「図 5.1. 各種インターフェースの配置」にピン配置図を追加</li> <li>「5.12. CON11(LAN コネクタ)」に PHY の割り込み信号についての記述を追加</li> <li>「6.3. LED(D1, D2)」に「6.3.1. 基板リビジョン E 以前のLED(D2)仕様」と「6.3.2. 基板リビジョン E 以後のLED(D2)仕様」を追加</li> <li>「Flash メモリ」を「フラッシュメモリ」に統一</li> </ul> |

| 1.0.8 | 2007.9.14  | <ul><li>・「2.2. 保証に関する注意事項」を追加</li><li>・「2.2. 取扱い上の注意事項」 に改造した場合の保証について追加</li><li>・「5.2. CON1(シリアルインターフェース 1)」 の記述を変更</li></ul>                                                                                                                                                                                                                                                                                                      |

| 1.0.9 | 2007.10.19 | ・「5.2. CON1(シリアルインターフェース 1)」 の記述を変更                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.0.10 | 2007.12.14 | <ul><li>・表紙と「1. はじめに」 に ANO11 (PC104 コネクタ実装品)の記載を追加</li><li>・「7. 基板形状図」 を「7.1. ANO10 基板形状図」 と「7.2. ANO11 基板形状図」 の二つに変更</li></ul>                                                                                                                        |

|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0.11 | 2008.3.15  | ・「6.2. 外部割込みについて」 に注意事項を追加<br>・「図 6.2. EXTIRQ の接続」 に抵抗値の記述追加                                                                                                                                                                                            |

| 1.0.12 | 2008.9.26  | <ul><li>出力電圧の精度を追記</li><li>タイトルを英語表記からカタカナ表記に</li><li>「6.4. カレンダ時計(Real Time Clock)」RTC バックアップ用バッテリに関する注意事項を追記</li></ul>                                                                                                                                |

| 1.0.13 | 2008.12.25 | <ul> <li>・下記の画像形式を SVG に変更</li> <li>・・「図 3.1. Armadillo-9 ブロック図」</li> <li>・「図 5.2. PC/104 バスのメモリ空間」</li> <li>・「図 7.1. AN010 の基板形状」</li> <li>・「図 7.2. AN011 の基板形状」</li> </ul>                                                                            |

| 1.1.0  | 2009.03.19 | ・「1. はじめに」、「2. 注意事項」 構成変更<br>・誤記、表記ゆれ修正                                                                                                                                                                                                                 |

| 1.1.1  | 2009.07.17 | ・「5.16. J1, J2(PC/104 準拠拡張バス)」、「表 5.17. J1 信号配列<br>(1)」、「表 5.18. J1 信号配列(2)」PC/104 情報について修正<br>・本文のレイアウト統一<br>・表記ゆれを修正                                                                                                                                  |

| 1.1.2  | 2009.07.29 | ・製品保証に関する記載を http://www.atmark-techno.com/<br>support/warranty-policy に移動(2009/08/03 適用)                                                                                                                                                                |

| 1.1.3  | 2010.01.29 | <ul> <li>・本文のレイアウト統一</li> <li>・「表 5.1. 各種インターフェースの内容」「表 5.21. LED(D5,D6) の 状態」「表 5.22. LED(D14) の状態」「表 5.24. コネクタ/スイッチ型式の一覧」「表 5.25. LED型式の例」へッダの「記号」を「部品番号」に変更</li> <li>・VGA コネクタの名称を「D-Sub15 ピン、3 列」から「ミニ D-Sub15 ピン」に修正</li> <li>・表記ゆれを修正</li> </ul> |

| 1.1.4  | 2011.03.25 | <ul><li>・「2. 注意事項」を全面的に変更</li><li>・会社住所変更</li></ul>                                                                                                                                                                                                     |

| 1.1.5  | 2011.03.25 | ・「図 6.1. PC/104 の割り込みコントローラの仕組み」を変更し、マスクビットが"1"の場合の説明を追加・「表 5.17. J1 信号配列(1)」 ~ 「表 5.20. J2 信号配列(2)」に注釈を追加                                                                                                                                              |

| 1.1.6  | 2011.10.21 | ・Web サイトの名称を変更                                                                                                                                                                                                                                          |

|        | •          |                                                                                                                                                                                                                                                         |

Armadillo-9 ハードウェアマニュアル Version 1.1.6 2011/10/21

株式会社アットマークテクノ

060-0035 札幌市中央区北 5 条東 2 丁目 AFT ビル TEL 011-207-6550 FAX 011-207-6570